Chip designers do their best to use the latest cocktail of verification techniques and tools, and EDA companies continually innovate new verification tools, design flows, and pre-verified silicon IP, in a valiant effort to achieve the elusive goal of achieving chip design verification perfection.

High performance and high density

Automatic partitioning

Deep trace debug

Flexible & powerful I/Os

Flexibly design in various ways

Cycle and event driven mode

High speed simulation engine

Advanced modeling interface

RTL code analysis

Logic equivalent check

Vacuous assertion check

Verification progress and coverage measurement

Architecture design

System performance analysis logic equivalent check

Virtual devices

IP modeling in early design stage

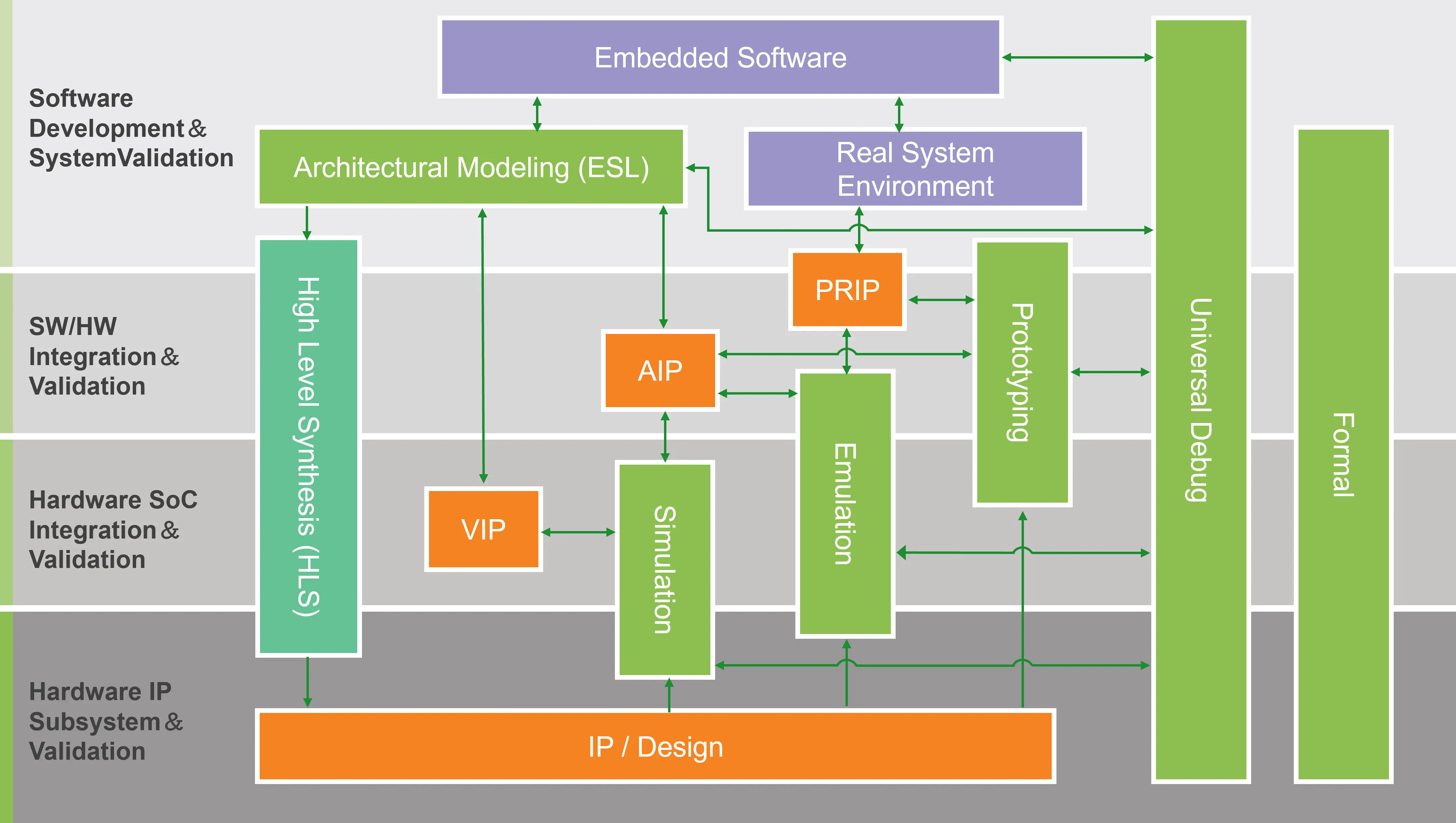

The increasing size and complexity of SoC/ASIC designs have led to an exponential increase in the complexity of validation. In order to reduce time to market, it is important to choose different verification tools in different design stages to improve efficiency and accelerate the convergence of verification.

Design architecture planning, system performance analysis, virtualization application scenarios and IP modeling in the early stage

Support SystemVerilog, Verilog and VHDL RTL level simulation

Hardware simulation accelerates super-large design simulation speed and supports automatic compilation and full signal visibility

High-performance prototype verification for early software development and extensive system testing

Use transaction-level interfaces to reduce test program development time while ensuring the accuracy of system results