# PROTOTYPICAL

## The Emergence of FPGA-Based Prototyping for SoC Design

#### **Includes All-New**

Field Guide

## DANIEL NENNI & DON DINGEE

A SEMIWIKI PROJECT

## PROTOTYPICAL

### The Emergence of FPGA-based Prototyping for SoC Design

Foreword by Mon-Ren Chene, CTO of S2C Inc.

Daniel Nenni Don Dingee @2016 by Daniel Nenni and Don Dingee

All rights reserved. No part of this work covered by the copyright herein may be reproduced, transmitted, stored, or used in any form or by any means graphic, electronic, or mechanical, including but not limited to photocopying, recording, scanning, taping, digitizing, web distribution, information networks, or information storage and retrieval systems, except as permitted under Section 107 or 108 of the 1976 US Copyright Act, without the prior written permission of the publisher.

Published by SemiWiki LLC Danville, CA

Although the authors and publisher have made every effort to ensure the accuracy and completeness of information contained in this book, we assume no responsibility for errors, inaccuracies, omissions, or any inconsistency herein.

Custom printed for S2C at DAC 2016 by OneTouchPoint, Austin TX

First printing: June 2016 Printed in the United States of America

"Implementing an FPGA Prototyping Methodology" Field Guide included with permission of S2C, Inc.

Edited by: Shushana Nenni

#### Contents

| Foreword                                      | v  |

|-----------------------------------------------|----|

| The Future of FPGA Prototyping                | v  |

| Design for FPGA Prototyping                   | v  |

| Moving to the Cloud                           | ix |

| Introduction: The Art of the "Start"          | 1  |

| A Few Thousand Transistors                    | 2  |

| Microprocessors, ASICs, and FPGAs             | 5  |

| Pre-Silicon Becomes a Thing                   | 7  |

| Enabling Exploration and Integration          | 10 |

| Chapter 1: SoC Prototyping Becomes Imperative | 15 |

| Programmable Logic in Labs                    | 15 |

| First Productization of Prototyping           | 18 |

| Fabless and Design Enablement                 | 20 |

| Chapter 2: How S2C Stacked Up Success         |    |

| Making ESL Mean Something                     | 25 |

| TAI IP and "Prototype Ready"                  | 26 |

| Taking on the Cloud                           | 30 |

| Chapter 3: Big EDA Moves In                   |    |

| A Laurel and HARDI Handshake                  |    |

| Verification is Very Valuable                 |    |

| An Either-Or Response                         |    |

| A Bright Future Ahead                         | 41 |

| Chapter 4: Strategies for Today and Tomorrow  | 45 |

| The State of FPGA-Based Prototyping           | 45 |

| Developing for ARM Architecture               | 48 |

| Adoption Among Major System Houses            | 51 |

| Application Segments in Need                  | 52 |

| FIELD GUIDE                                          | 59  |

|------------------------------------------------------|-----|

| When Do You Need an FPGA-based Prototyping Solution? | 61  |

| How Do I Choose Which Solution to Implement?         | 64  |

| Building a Scalable Prototyping Platform             | 69  |

| Overview of the FPGA Prototyping Methodology Flow    |     |

| Details of Implementing the FPGA Prototyping Flow    | 81  |

| Exercising the Design                                | 97  |

| Coding with FPGA-based Prototyping in Mind           | 104 |

About the Authors

#### Foreword

#### The Future of FPGA Prototyping

Nearly two decades ago during our time at Aptix, my S2C co-founder, Toshio Nakama and I recognized the power of prototyping. At that time, prototyping was only accessible by large design houses with the budget and means to employ a prototyping architecture. We also recognized that FPGAs had become a popular alternative to the much more expensive and rigid ASICs. It was then that we both decided to team up to develop a prototyping board around an FPGA, and S2C was born. Our commitment to our customers has been to push the limits of what FPGA prototyping can do to make designing easy, faster, and more efficient. Our goal has always been to close the gap between design and verification which meant that we needed to provide a complete prototyping platform to include not only the prototyping hardware but also the sophisticated software technology to deal with all aspects of FPGA prototyping.

Fast forward to today and you'll find that FPGAs and FPGA prototyping technology has advanced so much that designers and verification engineers can no longer ignore the value that they bring, especially when dealing with the very large and complex designs that we see today. These advances have made FPGA prototyping poised to become a dominant part of the design and verification flow. This book will hopefully give you a sense of how this is achieved.

But what's next for FPGA prototyping? Having dedicated my time to working with our customers in developing the evolution of FPGA prototyping, I have figured out two things: FPGA prototyping needs to be part of the conversation early on in the design process, and FPGA prototyping needs to move to the cloud.

What do I mean by these two statements? Well, let's break it down.

#### **Design for FPGA Prototyping**

Making FPGA prototyping part of the design process early means actually thinking about how the design will be prototyped via an FPGA

as you design – Design for FPGA Prototyping. Designing for prototyping will significantly speed up the FPGA prototyping process downstream. It will aid in the act of synthesis, partitioning, and debug. I've outlined six ways that this is achieved:

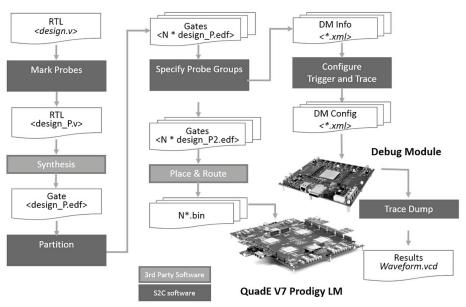

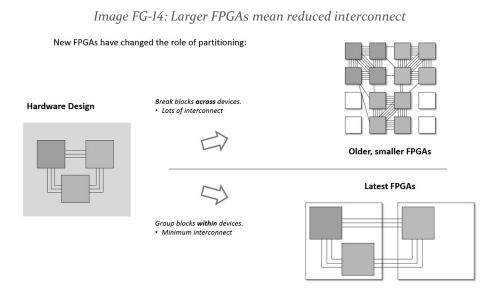

#### 1) Prototyping-friendly Design Hierarchies

Design architects can make the job of prototyping much easier for engineers to implement FPGA prototyping by modifying the design hierarchy to work better in a prototyping environment. The engineers who perform implementation or verification usually have very little ability to improve prototyping performance once the design hierarchy is fixed. The need to do partitioning down to the gate level can be removed if the size of each design block can be kept to one FPGA. Furthermore, modifying the design hierarchies early can help to avoid pin congestion as many times a design becomes very difficult to implement in an FPGA or becomes very slow because there's a central block that has tens of thousands of signals that need to go to multiple blocks in different FPGAs. Design architects can also ease prototyping by providing guidance to their FPGA implementation team(s).

#### 2) Block-based Prototyping

Instead of hoping the entire design will magically work when mapped and downloaded to multiple FPGAs, bringing up subsystems of the entire design, block by block, will allow quick identification of both design issues in a sub-block as well as any issues related with mapping the design to the FPGA(s). Blockbased prototyping works well especially with designs that contain many 3rd party IPs that also needs a lot of real time testing and early software development.

And very often, designers don't even have the RTL source code for the IP blocks from 3rd parties (for example, ARM processors) and therefore cannot map the IP to the FPGAs themselves. This can be solved by requesting the IP provider to supply the encrypted netlist so that you can synthesize and partition the entire design while treating that IP as a black-box. As long as you specify the correct resources (LUT, registers, I/Os), the prototype compile software should take those resources into account when partitioning to multiple FPGAs. You can then integrate the encrypted netlist during the place and route stage.

I've come across customers that want to do an FPGA implementation but are reusing some very old blocks with only the ASIC netlist and without RTL. Implementation becomes very difficult since the details of the design are unknown. These legacy designs are usually only accompanied by a testbench. In this case, the best approach is to covert the ASIC gates to an FPGA and to use a co-simulation environment (such as S2C's ProtoBridge<sup>™</sup>) to verify if the functionality of the block is correct before integrating it with the entire design. Unfortunately, this is still a painful process so designers should consider either not using those legacy blocks or re-writing them.

Note that a reconfigurable and scalable prototyping system is needed for a block-based prototyping methodology, as well as a robust partitioning and FPGA prototyping software flow.

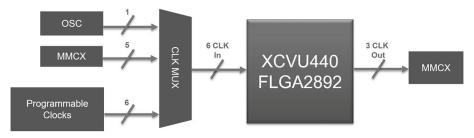

#### 3) Clean and Well-defined Clock Network for Prototyping

Many ASIC designs have tens or even hundreds of clocks and most of them are just for power management/saving. Even with the most complex designs there are usually a few real system clocks plus some peripheral clocks such as PCIe and DDR. Peripheral clocks usually reside in a single FPGA which has the actual external interface pins and therefore are easy to implement. System clocks, however, need to go to every FPGA and therefore should be clean for FPGA implementation.

ASICs use a lot of gated clocks to save power. Today's FPGA synthesis tools have advanced to take care of most of the gated clocks, but there may still be some gated clocks that go undetected and therefore cause design issues. This can easily be avoided by creating two different RTL clock implementations for the ASIC and the FPGA by using IFDEF. Internally generated clocks can also be a problem for an FPGA prototyping environment as they all need to get on the FPGAs' global clock lines and synchronize among all the FPGAs. A Multi-FPGA prototyping system will have a limitation on how many of these global clocks can be supported therefore the number of the internally generated clocks should be restricted (or again use two implementations in the RTL: one for ASIC, and one for FPGA).

#### 4) Memory Modeling

ASICs support many different types of memories while FPGAs usually support two types: synchronous dual port memories, or the use of registers and LUTs to build custom memories. The latter one consumes large amounts of logic resources and might cause place and route congestion. Most ASIC memories can be re-modeled to take advantage of the block memories in the FPGA but a manual process may be required to do that. Again, instead of having the engineers who try to implement the ASIC design in a FPGA model the memories, a better approach would be to have the architects plan the designs with two memory implementations both for ASICs and FPGAs. The RTL designers then code using IFDEF to have the two implementations. FPGA prototyping becomes easy by just instantiating the correct memory implementations.

#### 5) Register Placement on the Design Block I/Os

FPGAs usually have a lot of register resources available for the design but most ASIC designs try to use less registers to save area and power. Ideally, all block I/Os should be registered for FPGA implementation to achieve the best results. At a minimal all outputs should be registered so no feed-through nets (which impact system performance by half) will be created after design partitioning. As a result, there will be a noticeably higher FPGA prototyping performance with this approach.

#### 6) Avoid Asynchronous or Latch-based Circuits

Asynchronous circuits and latch-based designs are FPGA unfriendly. It is very hard to fine-tune timing in an FPGA with every FPGA having to be re-place and re-routed multiple times. These issues become even worse when the asynchronous circuits have to travel across multiple FPGAs.

#### Moving to the Cloud

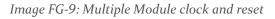

We are living in an age where design teams no longer reside in one geographic location. No matter how big or small, companies have multiple design teams in multiple locations. A cloud-based FPGA prototyping system is an ideal way for dispersed teams to manage the prototyping process and resources.

Furthermore, as smaller IoT designs proliferate the market, FPGA prototyping must become accessible to these designers. Today's FPGA prototyping, although effective, can be costly for smaller IoT designers to adopt. The reusability of boards becomes less viable so costs cannot be amortized over multiple design starts. By moving to the cloud, FPGA prototyping solutions can become a shared resource and thus can reduce cost inefficiencies.

The future of FPGA prototyping is strong. It has and will continue to demonstrate itself as one of the most effective solutions to realizing the full potential of any design.

Mon-Ren Chene CTO of S2C, Inc. May 2016

#### Introduction: The Art of the "Start"

The health of the semiconductor industry revolves around the "start". Chip design starts translate to wafer starts, and both support customer design wins and product shipments. Roadmaps develop for expanding product offerings, and capital expenditures flow in to add capacity, enabling more chip designs and wafer starts. If all goes according to plan, this cycle continues.

In the immortal words of an engineering manager from once upon a time, "You didn't say it has to work." Chip designs have progressed from relatively simple to vastly complex and expensive, and the technology to fabricate them has shrunk from dimensions measured in tens of microns to tens of nanometers. Functions once dictated by distinctive symbols and lines or ones and zeroes in a table now center on executing powerful operating systems and application software and streams of rapidly flowing data.

Keeping the semiconductor cycle moving depends on delivering complex chip designs, completely verified with their intended software environment, faster and more accurately. Wafer fab facilities now approach tens of billions of dollars to construct and equip, producing massive high-capacity wafers. One malevolent block of logic within a chip design can cause expensive wafers to become scrap. If that flaw manages to escape, only showing itself in use at a critical moment, it can set off a public relations storm questioning a firm's design capability.

Verification is like quality: either it exists, or it does not. Only in a context of project management does partial verification of a design mean anything.

With the stakes so high for large, sophisticated chips, no prudent leader would dare avoid investments in semiconductor process quality. Foundries such as GlobalFoundries, Intel, Powerchip, Samsung, SMIC, TSMC, UMC, and others have designed entire businesses around producing quality in volume at competitive costs for their customers. Yet, chip design teams often struggle with justifying verification costs, settling for doing only part of the job. A prevailing assumption is the composite best efforts of skilled designers using powerful EDA tools should result in a good design. Reusing blocks from known-good sources, a long-standing engineering best practice in reducing risk and speeding up the design cycle, helps.

Any team that has experienced a chip design "stop" knows better. Many stories exist of a small error creeping through and putting a chip design, and sometimes a reputation, at risk. The price of nonverification of both hardware and software of a design can dwarf all other investments, and instantly thwart any prior success a firm may have enjoyed.

This is where FPGA-based prototyping comes in. A complete verification effort has traceable tests for all individual intellectual property (IP) blocks and the fully integrated design running actual software (co-verification), far beyond what simulation tools alone can do in reasonable time. Hardware emulation tools are capable, fast, but highly expensive, often out of reach for small design teams. FPGA-based prototyping tools are scalable, cost-effective, offer improved debug visibility, and are well suited for software co-verification and rapid turnaround of design changes.

In this book, we uncover the history of FPGA-based prototyping and three leading system providers – S2C, Synopsys, and Cadence. First, we look at how the need for co-verification evolved with chip complexity, where FPGAs got their start in verification, and why ASIC design benefits from prototyping technology.

#### A Few Thousand Transistors

One transistor came to life at Bell Labs in 1947. Solid-state electronics held great promise, with transistors rapidly improving and soon outperforming vacuum tubes in size, cost, power consumption, and reliability. However, there were still packaging limitations in circuit design, with metal cans, and circuit boards and wires, and discrete passive components such as resistors and capacitors. <sup>1</sup>

In 1958, Jack Kilby of TI demonstrated a simple phase-shift oscillator with one bipolar transistor and roughly hewn resistors and capacitors on one slice of germanium, with flying wire connections on the chip. By 1960, Fairchild teams led by Robert Noyce had a monolithic integrated four-transistor flip-flop running in silicon, a more stable and mass-producible material and process. <sup>2, 3</sup>

Standard small-scale integration (SSI) parts appeared in 1963, with Sylvania's SUHL family debuting as the first productized TTL family. TI followed with the military grade 5400 Series and the commercial-grade 7400 Series, setting off a parade of second-sourcing vendors. In rough terms, these SSI parts used tens of transistors providing a handful of logic gates. <sup>4</sup>

Medium-scale integration (MSI) first appeared with the 4-bit shift register – a part that Irwin Jacobs of Qualcomm fame proclaimed in a 1970 conference as "where it's at" for digital design. MSI parts with hundreds of transistors extended the productized logic families with a range of functions, but were still simple to use. Where SSI parts offered several individual gates in a single package with common power and ground, MSI parts usually grouped gates into a single functional logic block operating on multiple bits of incoming data. Pin counts and package sizes remained small.

SSI and MSI parts are the electronic equivalent of hand-chiseled statues. Producing a mask was labor-intensive, with layouts carefully planned and checked by engineers. Vendors heavily parameterized parts across variables of voltage, temperature, rise and fall time, propagation delay, and more. Each chip was a small block of IP, taken as golden, assembled into a system using wire wrapping or stitching for prototypes or short runs, and printed circuits for finished product in higher volumes. Everything about an SSI or MSI design was readily visible just by probing with an oscilloscope or logic analyzer at the package pins, and problems were usually somewhere in the wires in between.

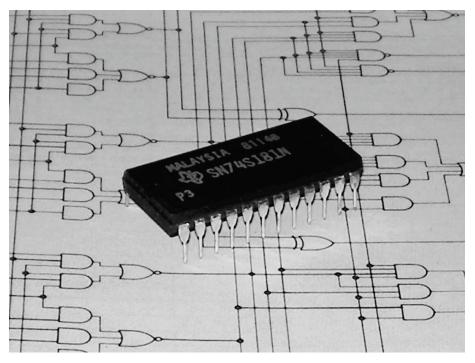

Image I-1: Texas Instruments SN74SI8IN 4-bit ALU with 63 logic gates

That changed drastically when large-scale integration (LSI) parts emerged. The early 1970s saw chips for digital watches, calculators, and the first integrated computer memories, each with a few thousand transistors. LSI parts were analogous to Mount Rushmore – carved from the monolith in labor-intensive steps. Parts were harder to verify post-layout, and more expensive to fabricate. Packaging changed as chips had significantly more I/O pins. Second-sourcing became less common as vendors protected their high-value IP.

Using LSI chips changed as well. The good news was more functions were integrated. The bad news was board-level test visibility declined, with designers having to trust the data sheet because the inner workings of a chip were mostly impenetrable. Chip errata become commonplace; instead of fixing the chip layout immediately, vendors spent energy on diagnosing issues and determining workarounds, waiting to gather enough fixes to justify a chip respin.

#### Microprocessors, ASICs, and FPGAs

Entire "processors" combined LSI, MSI, and SSI chips. A prime example was a Linkabit design in 1971 for a Viterbi decoder – 360 TTL chips on 12 boards, in a single 4.5U rackmount enclosure replacing a couple cabinets of earlier equipment. Assembly language programming took shape, with simple instruction sets. This was exactly the transformation Jacobs had been talking about, but his firm and many others were looking beyond, to bigger chips that consolidated functions. <sup>5</sup>

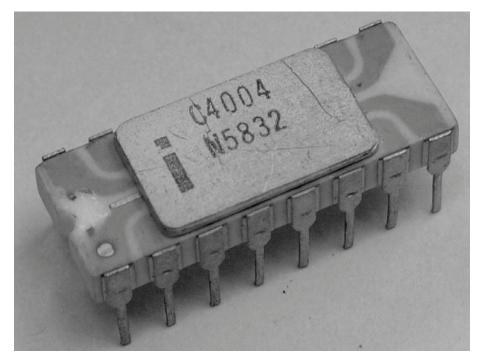

Image I-2: Intel 4004 microprocessor

Intel moved to the lead in LSI with offerings in DRAM, EPROM, and a new type of chip in November 1971: the microprocessor. Its first part sprang from a custom product for a Japanese calculator vendor. The 4004 4-bit microprocessor debuted under the MCS-4 banner, including RAM and ROM and a shift register tuned for the 4-bit multiplexed bus. With 2300 transistors fabbed in 10 micron and running up to 740 MHz, the 4004 had 16 internal registers and offered 46 instructions. <sup>6</sup>

Feverish competition ensued as a slew of vendors created new 8-, 16-, and 32-bit microprocessor architectures during the late 1970s and early 1980s. Even with lengthy schedules and meticulous design checking, very few of these complex chips worked the first time. Design and fab costs continued escalating as transistor counts moved into the tens of thousands and beyond.

Most of these microprocessor vendors had large fabrication facilities and proprietary design flows tuned to their engineering standards and fabrication process. A sea change was occurring in VLSI (very large scale integration), with several technological advances opening the way for new vendors.

The first usage of ASICs was as glue logic for improved integration, or as companion chipsets to microprocessors, often customized to a specific board design. A growing roster of ASIC vendors eventually including AT&T, Fujitsu, IBM, LSI Logic, Plessey, Toshiba, TI, and VLSI Technology were working to abstract the design flow with tools, IP libraries, and fab qualification. For the first time, design teams at a customer could create parts using "standard cells" and get them produced at moderate risk and reasonable lead times of a few months.

The average 32-bit microprocessor trended toward bloated, with more transistors to execute maddeningly complex instruction sets (CISC) with routine and not-so-routine operations and specialized addressing modes. Researchers tore into the flow of instructions, deciding that only a few mattered, and came up with the idea of Reduced Instruction Set Computing, or RISC. ASICs and RISC were a match made in heaven, and MIPS Computer Systems, Sun Microsystems, and others soon burst on the scene with new processor architectures.

Another breakthrough was near. Altera took an idea from the research halls of GE, combining the elements of EPROM memory with CMOS floating logic gates, and added synthesis software in 1984. A logic design for the Altera EP300 could be created on a PC in a week or so using schematic capture, state machine, or logic table entries. Parts could be "burned", and easily erased with an ultraviolet light and reprogrammed as needed, in a matter of hours. Customers with conventional digital logic schematic entry skills had access to relatively high customization with very low turnaround time. <sup>7</sup>

Image I-3: Altera EP300 programmable logic device

A different technology appeared on November 1, 1985, with the thundering headline, "Xilinx Develops New Class of ASIC". The XC2064 logic cell array was RAM-based, loading its configuration at boot time. Soon to be labeled by the media as a field programmable gate array or FPGA, these first parts featured 1200 gates, offering more scalability and higher performance. Logic could be simulated on a PC, and in-circuit emulation aided in functional verification. <sup>8</sup>

#### **Pre-Silicon Becomes a Thing**

With programmable logic in its infancy, VLSI designs were still territory for ASICs. Even moderate risk using ASIC technology was still significant. The SPARC I processor took four respins to get right. In contrast, the ARMI processor at Acorn Computers powered up and ran on its first arrival from VLSI Technology in April 1985 – a minor miracle that shocked its creators, and still stirs amazement.

EDA tools from pioneers Daisy, Mentor, and Valid were being adapted from circuit board design to ASIC tasks. Rather than capturing a design

and tossing it into silicon and hoping for good results, more emphasis was being placed on logic simulation. EDA workstations were relatively fast, but simulation of a VLSI design was still a tedious and slow process, requiring skill to create a testbench providing the right stimuli. Still, ASIC simulation was cheaper than a failed piece of silicon and more dollars and several more months waiting for a fix. <sup>9</sup>

Major innovation was happening at Intel. Thanks to success in PC markets, its microprocessor families progressed rapidly. Design of the first mainstream PC processor, the 8088 released in 1979, involved painstaking human translation of logic gate symbols into transistors. For the 80286 debuting in 1982, an RTL (register transfer level) model drove high-level design and timing analysis, but manual translation into transistor structures was still necessary. The 80386 launched in 1985 saw wider use of RTL synthesis and a move toward CMOS standard cells, with only several specific logic blocks hand optimized.

If Intel was to keep its winning streak going, development processes had to change to shorten the cycle time for increasingly complex parts. Beginning in 1986, Intel made a \$250M investment for its next microprocessor design, including a proprietary system of EDA tools and practices. To enable fully automatic synthesis of layout from RTL, teams created iHDL, built logic synthesis tools from code developed at the University of California, Berkeley, and formalized and extended the standard cell library. The result was the 80486, breaking the 1 micron barrier with a staggering 1.18M transistors in 1989.<sup>10</sup>

Just as ASIC vendors discovered, Intel found simulation too slow and falling further behind. RTL simulations were chewing up more than 80% of Intel's EDA computing resources, and verification was growing non-linearly with processor size. A solution would come from an unexpected source: the FPGA community.

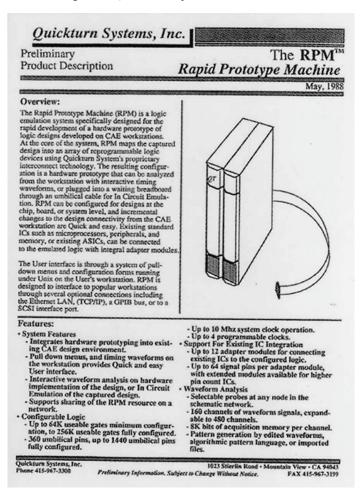

In May 1988, a small company – Quickturn Systems – introduced a new type of development platform aimed at ASIC designers. The Rapid Prototype Machine (RPM) used an array of Xilinx XC3090 FPGAs in a hypercube interconnect. Its software could take an ASIC netlist of hundreds of thousands of gates, partition it into the FPGA array, and

emulate the design up to a million times faster than software simulation.  $\ensuremath{^{11}}$

Image I-4: Quickturn Systems RPM datasheet

At those speeds, much more serious pre-silicon testing became feasible. Intel embraced the concept, putting its new P5 microarchitecture through its paces on a cluster of 14 Quickturn RPM systems – 7 for integer operations, 4 for caches, and 3 for floating point. In a November 1991 demonstration, an Intel VP ran a Lotus 1-2-3 spreadsheet on a P5 model in the Quickturn cluster. Customers considering RISC processors shelved plans, opting to wait for Intel to deliver. <sup>12</sup> Running trillions of simulation clocks in this environment, Intel was able to debug development tools and clobber several errata and various operating system incompatibilities before committing to expensive silicon. More importantly, the effort sawed several months off their development schedule, leading to a timely release of the Pentium microprocessor in March 1993. <sup>13</sup>

#### **Enabling Exploration and Integration**

Strictly speaking, although it deployed Xilinx FPGAs and was essential in prototyping ASICs, the Quickturn RPM was the first commercial hardware emulator. From that point, advanced hardware emulator and FPGA-based prototyping platforms developed, on divergent paths for different use cases.

Hardware emulators are automatic, meant for big projects and broader application on more than one design. A user need not know details of the logic implementation, or how interconnects are organized. An arbitrary netlist for an ASIC is loaded, chopped into many smaller pieces, and spread out across many partitions – in the beginning, implemented with tens or hundreds of FPGAs.

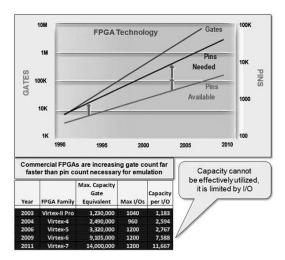

These partitions are subject to a relationship known as Rent's Rule, describing a necessary ratio of logic gates to interconnect pins. Paradoxically, as FPGA logic capacities improved, pin counts fell behind and Rentian interconnect limitations worsened, requiring even more FPGAs to accommodate large netlists. Eventually, emulator providers moved from FPGAs to ASIC-based designs. The price of tossing more hardware at the problem is steep, however: today's high performance hardware emulator can cost over \$IM.

Prototypes are more specific, often configured and tuned for one project. Assuming adequate logic capacity and interconnect pins, a design can be synthesized for a single FPGA target, or perhaps partitioned across a handful of FPGAs with optimized interconnect. Rent's Rule becomes less applicable for a design of manageable size. This is the basic premise of FPGA-based prototyping, which becomes more and more attractive as FPGA logic capacities improve. <sup>14</sup>

Image I-5: FPGA gates versus pin count, courtesy Cadence

What really makes the case for FPGA-based prototyping is not a change in FPGAs, however, but changes in system design practices and objectives. The type of design starts typical in the industry evolved dramatically, looking less often like an enormous Intel microprocessor. System-on-chips, microcontrollers, application-specific standard product (ASSPs), and other designs take advantage of a growing field of IP for customized implementations.

Reuse and integration is now paramount. Using FPGA-based prototyping, stand-alone verification of individual IP blocks is costeffective. Third-party IP, existing internally designed IP blocks, and new internal development can then be combined, with partitioning and test artifacts reused to aid in the process.

Design exploration is feasible, especially for software teams that can afford to place FPGA-based prototyping platforms on desks. What-if scenarios run at IP-block level can explore software tradeoffs or minor hardware architectural tradeoffs, not just functional fixes. These results can be rolled up quickly to the full-up design, perhaps resulting a critical product enhancement pre-silicon.

More FPGA-based prototyping platforms are integrating actual I/O hardware, usually with a mezzanine-based approach, instead of

emulating I/O with a rate-adapter of some type. This is an important factor for complex interface and protocol verification. It can also be a deciding factor in safety-critical system evaluation, where validation using actual hardware is essential.

At the high end, FPGA-based prototyping is scaling up. Platform-aware synthesis is improving partitioning across multiple FPGAs, allowing larger ASIC designs to be tackled. Cloud-based technology is connecting platforms and designers via networks. Debug visibility is increasing, with approaches including deep-trace capture and automatic probe insertion. Integration with host-based simulation and graphical analysis tools is also improving steadily.

The inescapable conclusion is if a chip project is to "start", it had better finish with robust silicon quickly. New applications, particularly the Internet of Things, may reverse a trend of declining ASIC starts over the last decade. Design starts are likely to be smaller and more frequent, with highly specialized parts targeting niches. Advanced requirements in power management, wireless connectivity, and security are calling for more intense verification efforts.

FPGA-based prototyping, as we shall see shortly, is rising to these challenges for a new era of chip design.

#### NOTES

<sup>1</sup> "1947 – Invention of the Point-Contact Transistor", Computer History Museum,

http://www.computerhistory.org/semiconductor/timeline/1947invention.html

<sup>2</sup> "1958 – All semiconductor 'Solid Circuit' is demonstrated", Computer History Museum,

http://www.computerhistory.org/semiconductor/timeline/1958-Miniaturized.html

<sup>3</sup> "1960 – First Planar Integrated Circuit is Fabricated", Computer History Museum,

http://www.computerhistory.org/semiconductor/timeline/1960-FirstIC.html

<sup>4</sup> "1963 – Standard Logic IC Families Introduced", Computer History Museum,

http://www.computerhistory.org/semiconductor/timeline/1963-TTL.html

<sup>5</sup> "Viterbi Decoding for Satellite and Space Communication", Jerry Heller and Irwin Jacobs, Linkabit Corporation, IEEE Transactions on Communication Technology, October 1971, pp. 835-848,

http://ieeexplore.ieee.org/xpl/login.jsp?tp=&arnumber=1090711 6 "The Story of the Intel 4004", Intel,

http://www.intel.com/content/www/us/en/history/museum-story-ofintel-4004.html

<sup>7</sup> "In the Beginning", Ron Wilson, Altera,

https://www.altera.com/solutions/technology/systemdesign/articles/ 2013/in-the-beginning.html

<sup>8</sup> "XILINX DEVELOPS NEW CLASS OF ASIC.' Blast from the Past: A press release from 30 Years ago, yesterday", Steve Leibson, Xilinx, November 3, 2015, <u>https://forums.xilinx.com/t5/Xcell-Daily-</u>

<u>Blog/XILINX-DEVELOPS-NEW-CLASS-OF-ASIC-Blast-from-the-Past-</u> <u>A-press/ba-p/663224</u>

<sup>9</sup> "A Brief History of ASIC, part I", Paul McLellan, SemiWiki, August 21, 2012, <u>https://www.semiwiki.com/forum/content/1587-brief-history-asic-part-i.html</u>

<sup>10</sup> "Coping with the Complexity of Microprocessor Design at Intel – A CAD History", Gelsinger et al, Intel, IEEE Solid-State Circuits Magazine, June 2010,

http://webee.technion.ac.il/people/kolodny/ftp/IntelCADPaperFinal2. pdf

<sup>n</sup> "A Reprogrammable Gate Array and Applications", Stephen Trimberger, Xilinx, Proceedings of the IEEE, Vol. 8l No. 7, July 1993, <u>http://arantxa.ii.uam.es/~die/[Lectura%20FPGA%20Architecture]%20</u>

<u>A%20reprogrammable%20gate%20array%20-Trimberger.pdf</u>

<sup>12</sup> "Inside Intel", Robert Hof, BusinessWeek, June 1, 1992, <u>http://www.businessweek.com/1989-94/pre88/b326855.htm</u>

<sup>13</sup> "Pre-Silicon Validation of Pentium CPU", Koe et al, Intel, Hot Chips 5, August 10, 1993, <u>http://www.hotchips.org/archives/1990s/hc05/</u>

<sup>14</sup> "Logic Emulation and Prototyping: It's the Interconnect (Rent Rules)", Mike Butts, NVIDIA, RAMP at Stanford, August 2010, <u>http://ramp.eecs.berkeley.edu/Publications/RAMP2010\_MButts20Aug</u> %20(Slides,%208-25-2010).pptx

#### Chapter 1: SoC Prototyping Becomes Imperative

Electronic design was changing in the mid-1980s. Brute force schematic capture was being supplanted by logic synthesis from hardware description language. Wire wrapping or stitching techniques for prototyping were being rendered obsolete as denser, higher pin count packages appeared. Printed circuit board technology was advancing rapidly, hand in hand with microprocessors, more complex ASIC parts, and new FPGA technology.

Competing to launch products on time meant creating chip designs faster. While hardware emulation proved very useful in ASIC verification, it was prohibitively expensive for smaller use cases. Sometimes, students and engineers just wanted to tinker with a design in a lab to prove a concept, or had only small production volumes in mind. If a project could bear the moderate cost of an FPGA, it was an ideal vehicle for experimentation. Two new use cases emerged for FPGAs: reconfigurable computing, and rapid prototyping.

#### Programmable Logic in Labs

Reconfigurable computing was the holy grail for signal processing, an ideal application for FPGAs with DSP-like primitives. An FPGA card could be added as a co-processor to an engineering workstation, and its logic architected to provide efficient data flow computational capability. The same workstation and FPGAs could be reconfigured for different applications quickly, especially if Xilinx SRAM-based FPGA technology were used.

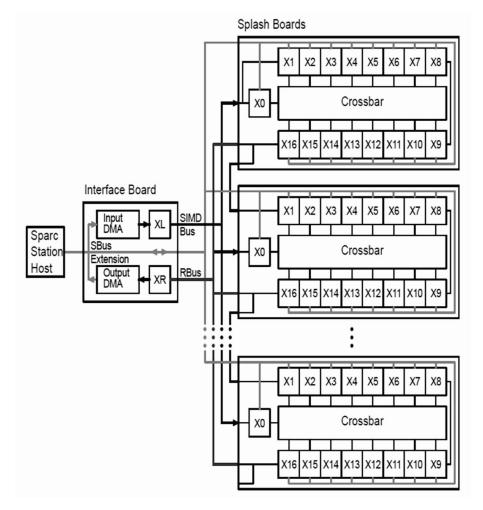

Prime examples of early reconfigurable computing platforms were Splash 1 and Splash 2, originally created to perform DNA sequence comparison. Created in 1988, Splash 1 was a VMEbus system with 32 Xilinx XC3090 FPGAs in a linear systolic array. While powerful, the Splash 1 architecture quickly proved to be limited by the available FPGA interconnect, typically in the range of 200 to 300 pins and subject to clocking and delay variables.

Splash 2 began in 1991, upgrading to XC4010 FPGAs with a crossbar interconnect. It allowed chaining of up to 16 array boards each with 16

processing FPGAs (with a 17<sup>th</sup> part controlling the crossbar), and added an SBus adapter for easy connection to a Sun Microsystems SPARCstation. <sup>15</sup>

Image 1-1: Splash 2 block diagram

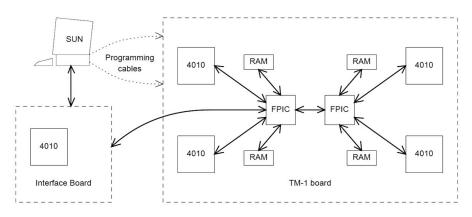

Interconnect in hardware emulators and reconfigurable systems was becoming a hot topic. A new technology debuted in 1992, the Aptix FPIC (field programmable interconnect chip). Aptix parts used similar SRAM-based technology to provide around 1000 interconnect pins sans logic, somewhat relaxing Rent's Rule limitations and allowing much more flexible configurations on a printed circuit board. FPICs were expensive, however, due to their high pin count packages. <sup>16</sup>

Academic researchers took these concepts in a new direction, scaling down to run HDL chip designs of a few thousand gates in smaller FPGA-based rapid prototype boards. The idea behind rapid prototyping was software would run immediately with full fidelity to production silicon – or not. If the project did not have access or could not afford to fabricate a chip, a rapid prototype could still prove the validity of the concept.

The first of these rapid prototyping boards appearing in 1990 was the AnyBoard from North Carolina State University. It returned to a simple linear array of five Xilinx XC3090s and soon added automated circuit partitioning built on Xilinx place & route software. The partitioning software understood interconnect pins, clock rates, and logic and I/O constraints. Researchers compared gradient descent algorithms with a multi-bin version of Kernighan and Lin graph partitioning, testing designs of varying complexity. <sup>17</sup>

Also in 1990, researchers at Stanford University created Protozone, a single Xilinx FPGA on a PC add-in card for experimentation. Protozone became a jumping-off point for other research projects in FPGA programming, but as a degenerate single-part configuration it did little to advance partitioning and routing science. However, it did spur broader educational programs at both Altera and Xilinx to provide simple, low-cost FPGA boards for prototyping. <sup>18</sup>

From the University of California, Santa Cruz came the aptly named BORG in 1992. Two Xilinx FPGAs contained logic, two more held reconfigurable routing, and a fifth performed configuration and interfacing to a PC host. Much of the research focused on the problem of pin assignment using bipartite graphs and new algorithms for a twocommodity flow solution. (In a bit of irony, the first BORG prototype itself was wire wrapped.) BORG illustrated the complexity of programmable interconnect between parts even with relatively small FPGA packages. <sup>19</sup> Another single-chip Xilinx XC3030 implementation debuted in 1993, the Generic Reusable Module (GERM) from Duke University. Researchers were promoting rapid design and prove out of subsystems, with concepts of VHDL design and IP reuse. Students were encouraged to build realistic designs in smaller pieces, then reuse those concepts for larger projects in subsequent courses that could still be completed in a semester. <sup>20</sup>

The growing popularity of the Aptix FPIC influenced the design of the Transmogrifier-1 at the University of Toronto in 1994. It indirectly scaled up the BORG concept, with four more powerful Xilinx XC4010 FPGAs interconnected by two FPICs, and a fifth FPGA providing the interface to a SPARCstation. Researchers used the platform to speed designs of three example projects: a Viterbi decoder, a memory organizer that emulated various configurations, and a logarithmic number system processor. Using SRAM blocks in the FPGAs allowed algorithm optimization compared to full-custom chip designs (multichip modules using FPGA dies), resulting in higher clock speeds and other implementation insights that were fed back to future modules.<sup>21</sup>

Image 1-2: Transmogrifier-1 block diagram

#### First Productization of Prototyping

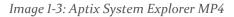

These research projects were stimulating broader interest and exploring critical issues in FPGA-based prototyping, but were far from ready for prime time. Hardware emulation still had a significant head start in commercialization. Aptix CEO Amr Mohsen reflected on the early business challenges with the FPIC parts, saying they were "probably two to three years ahead" and being asked by customers to move into complete, turnkey hardware emulation. At the Design Automation Conference in June 1994, Aptix launched two products. Explorer ASIC targeted single-chip emulation at 10 MHz using 21 Xilinx XC4000-class FPGAs and FPICs for interconnect, with automatic partitioning software provided by third party Software & Technologies. System Explorer MP3 provided general-purpose 50 MHz system-level emulation with configurable FPGA payloads and I/O, but lacking automatic partitioning tools. Automation would be added later with the System Explorer MP4 family in May 1996. <sup>22, 23</sup>

IKOS Systems bought its way into the hardware emulation market by acquiring Virtual Machine Works in May 1996. The VirtuaLogic SLI hardware emulator was productized and released by late 1996 with a basic 200K gate capacity upgradable to over 1M gates. VirtualWires technology created at MIT provided synthesis for FPGAs, avoiding a need to move toward ASICs as other vendors were doing. <sup>24</sup>

Major EDA players then moved in and competition got a bit ugly.

Meta Systems created the SimExpress emulator family in 1994, and after shopping itself to both Quickturn and Mentor Graphics agreed to a Mentor acquisition in May 1995. By early 1996, Quickturn and Mentor Graphics were involved in suit and countersuit over technology (some previously licensed to Quickturn in 1992), blocking sales of Meta Systems emulation platforms in the US for several years.

Mentor Graphics then licensed emulation technology from Aptix and promptly sued Quickturn again in 1998, unfortunately based on bogus claims in an Aptix engineering notebook. In a bid to resolve the patent issues, Mentor Graphics launched a hostile takeover for Quickturn in early 1998. It drew the attention of Cadence Design Systems, who raised the takeover offer to \$253M and secured Quickturn by December 1998. Legal wrangling continued. <sup>25</sup>

With the hardware emulation providers locked in expensive battles over high end platforms, the door was open for lower cost solutions from smaller providers. Gidel, based in Israel, converted its expertise in FPGA-based reconfigurable computing to a commercial FPGA-based ASIC prototyping board in 1998 featuring an Altera FPGA. Also in 1998 The Dini Group in the US took its ideas from ASIC design consulting into its first commercial FPGA-based prototype board, the DN250k10 with six Xilinx XC4085 FPGAs. <sup>26, 27</sup>

ASIC complexity in both gate and pin counts had overwhelmed most FPGA implementations, even attempts with programmable interconnect. HARDI Electronics AB, a small Swedish firm, reinvestigated the problem and decided to route FPGA I/O to high speed connectors leading off board. By insuring impedance and trace length matching, external cabling could be used to complete connections in the desired configuration. The result was the first HARDI ASIC Prototyping System (HAPS) created in 2000, based on the Xilinx Virtex FPGA. To get larger configurations, HARDI began work on a board stacking scheme and bus interconnect – HapsTrak.

#### Fabless and Design Enablement

The third major change in the industry was the rise of ARM processor core technology and a corresponding increase in foundry capability.

Powered largely by the meteoric rise of the ARM7TDMI core introduced in 1995, designers outside of the traditional semiconductor companies were gaining confidence in their ability to create producible chips, entirely fabless. <sup>28</sup>

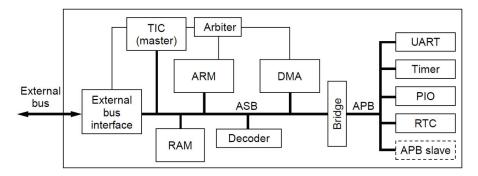

ARM understood that as their IP became more complex and foundries became more diverse, they needed to foster tools and methodology enabling their design customers to succeed. At first, ARM scaled via consulting in efforts led by Warren East beginning in 1994. Next, ARM introduced the Advanced Microcontroller Bus Architecture (AMBA) in 1997, seeking to standardize interconnect and make IP integration easier.

Image 1-4: AMBA system and peripheral buses, courtesy ARM

Then, ARM cores became fully synthesizable. The impetus was an effort at ASIC vendor LSI Logic who launched a CoreWare synthesizable version of ARM7TDMI in late 1997. ARM soon responded with standard synthesizable versions of its ARM7TDMI-S core and ARM946E-S and ARM966E-S macrocells, opening choices for using industry-standard EDA tools. By 2000, both TSMC and UMC had joined the new ARM Foundry Program and taken "per use" licenses.

Also in 2000, ARM made a strategic equity investment in CoWare and its IP models with an eye on providing more accurate simulations of the processor core. While useful, simulation was slow and models scarce, especially for many third-party peripheral IP blocks. Hardware emulation tools were prohibitively expensive for third-party peripheral block designers, often very small shops. However, a bigger opportunity was developing. An IP block could be fully tested standalone, but when integrated into a larger system-onchip with other peripheral blocks, new issues would develop. Either simulation would fail to uncover at-speed problems, or interaction between blocks would expose conditions untested in the standalone case.

The solution for affordable, faster, more complete testing of both IP blocks and integrated SoC designs was becoming FPGA-based prototyping. Both startups and larger EDA firms sought to capitalize on the trend.

#### NOTES

<sup>15</sup> "Reconfigurable Computing", Jeffrey M. Arnold, IDA Supercomputing Research Center, published in New Horizons of Computational Science: Proceedings of the International Symposium on Supercomputing, Tokyo, Japan, September 1997, edited by Toshikazu Ebisuzaki and Junichiro Makino, pp. 95-106.

<sup>16</sup> "The Roles of FPGAs in Reprogrammable Systems", Scott Hauck, Northwestern University, published in Proceedings of the IEEE, Volume 86 Issue 4, April 1998, pp. 615-638.

<sup>17</sup> "Automatic circuit partitioning in the AnyBoard rapid prototyping system", Douglas A. Thomae and David E. Van den Bout, North Carolina State University, Microprocessors and Microsystems, Volume 16 Issue 6, 1992, pp. 283-290.

<sup>18</sup> "Chips on the Net: An FPGA prototyping platform", M. J. Smith and H. Fallside, University of Hawaii and Xilinx, published in Proceedings of the 3<sup>rd</sup> European Workshop on Microelectronics Education, May 2000, pp. 151-154.

<sup>19</sup> "BORG: A Reconfigurable Prototyping Board Using Field-Programmable Gate Arrays", Pak K. Chan, Martine D. F. Schlag, and Marcelo Martin, University of California, Santa Cruz, published in Proceedings of the 1<sup>st</sup> International ACM/SIGDA Workshop on Field-Programmable Gate Arrays, 1992, pp. 47-51.

<sup>20</sup> "FPGA Based Low Cost Generic Reusable Module for the Rapid Prototyping of Subsystems", Apostolos Dollas, Brent Ward, John D. S. Babcock, Duke University, published in Lecture Notes in Computer Science, Volume 849, 1994, pp. 259-270.

<sup>21</sup> "The Transmogrifier: The University of Toronto Field-Programmable System", Galloway et al, University of Toronto, June 1994,

http://www.eecg.toronto.edu/~jayar/research/Transmogrifierl.pdf <sup>22</sup> "Aptix aims to be 'system-emulation' pioneer", Richard Goering, Techweb, CMP Publications, June 27, 1994, p. 33,

http://www.xsim.com/bib/papers.d/aptix.html

<sup>23</sup> "Aptix expands System Explorer family of emulation tools", Aptix press release, May 20, 1996,

http://www.thefreelibrary.com/APTIX+EXPANDS+SYSTEM+EXPLORE R+FAMILY+OF+SYSTEM+EMULATION+TOOLS-a018303369

<sup>24</sup> "Logic Emulation for the Masses Arrives; IKOS prepares to roll out production versions of its innovative VirtuaLogic SLI emulation

solution", IKOS Systems press release, September 16, 1996, <u>http://www.thefreelibrary.com/Logic+Emulation+for+the+Masses+Arrives%3B+IKOS+prepares+to+roll+out...-a018675799</u>

<sup>25</sup> "Too much preoccupation with patents?", Russ Arensman, embedded.com, January 1, 2003,

http://www.embedded.com/print/4347248

<sup>26</sup> Gidel web site, <u>http://www.gidel.com/ASIC-prototyping/index.asp</u>

<sup>27</sup> The Dini Group corporate presentation,

http://www.dinigroup.com/files/FPGA-based-

Cluster%20computing 9-09-10-HPC.pdf

<sup>28</sup> "Mobile Unleashed", Daniel Nenni and Don Dingee, SemiWiki, December 2015.

#### Chapter 2: How S2C Stacked Up Success

Startups are often pure-plays focused on a particular technology. When a new market opportunity appears, it is often startups who are able to move in first. Expertise gained in a previous round of technology development can propel a startup, with a new brand and strategy, from obscurity into prominence.

FPGA-based prototyping systems presented just such an opportunity. The groundswell in the IP ecosystem and the addition of foundry players in Asia brought a new audience of SoC designers into the mix. A wave of Asian firms, or Asian design centers for companies based in the US and Europe, were among the first ones open to new ideas and new EDA tools from a new innovator.

#### Making ESL Mean Something

Aptix had delivered outstanding FPGA interconnect technology, but as its legal issues deepened, it lost focus and became unable to compete for new business. By 2003 its key talent was defecting, ready to take the lessons learned from the reconfigurable computing days elsewhere.

Three ex-Aptix principals, Thomas Huang, Mon-Ren Chene, and Toshio Nakama pooled their own money to form S2C, Inc. – a creative spin on "system to chip". Based in San Jose, California, the vision for S2C was helping accelerate time-to-success for SoC design companies. To do that, S2C would need to build a new organization, and carefully craft and document their intellectual property to avoid the quagmire their previous engagement became mired in.

Focusing on the Chinese market as a major opportunity, S2C quickly set up its first offshore research and development center in Shanghai in 2003. This not only provided a talent pool, but also offered a way to connect and service customers based in Asia. Since the methodology behind FPGA-based prototyping was fairly new, and design teams using it were often working on small- or medium-sized projects, there would be a fair amount of customer handholding required. S2C was essentially in stealth mode for nearly two years. One of the key problems in making the leap from reconfigurable computing to FPGA-based prototyping was the tools used with FPGAs and the IP that went inside.

The buzzword making the rounds in EDA circles at the time was ESL: *electronic system-level* design. The idea of ESL sounded great on paper, bringing together approaches using high-level hardware descriptions with hardware and software co-design strategies and adding virtual prototyping and co-verification. (It was a lot of buzzwords inside buzzwords.) EDA vendors were scrambling to unify their tool suites and create a cohesive flow that shared design data and results.

FPGA tools were different, even foreign to most ASIC designers. For many, although the benefits of prototyping were increasing, the extra steps in becoming familiar with FPGA synthesis and debug were troubling. Worse yet, FPGA IP blocks were usually tuned for FPGA constructs. Steps to obtain logic and timing closure in FPGAs were different from those in ASICs. Concerns over the fidelity of an FPGAbased prototype were valid; if too much effort was required to resolve differences when moving a design back into an ASIC flow, the time-tosuccess gains from prototyping and exploration would be undone.

S2C's first task was to develop a complete methodology – a set of tools and IP that would not only make FPGA-based prototyping more productive, but would smooth out the transition of a design from the prototyping stage back into an EDA flow bound for an SoC.

## TAI IP and "Prototype Ready"

In February 2005, S2C filed its patent for a "Scalable reconfigurable prototyping system and method." It described a system for automating validation tasks for SoCs, with a user workstation, data communication interface, and an emulation platform with multiple FPGAs plus interfaces to a real-world target system. Its key observation was that SoC designs were composed of multiple IP blocks, and those could be synthesized from HDL into FPGAs, but needed some standardized method to communicate with a host for download, debug, and modification. <sup>29</sup>

A few months later, they gave a name to the concept: Testable, Analyzable, and Integratable IP, or TAI IP for short. A TAI IP block contained dynamically reconfigurable tag memory, multiplexers, buffers and latches, and could be added to user IP blocks to allow control and incremental run-time configuration. Both debug and performance analysis modes existed; for instance, a bandwidth analyzer mode could gather information on throughput and latency. <sup>30</sup>

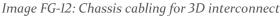

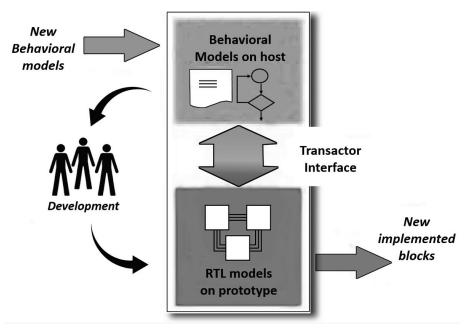

This allowed S2C to deliver a cohesive design flow. A top-level design including imported modules from HDL or netlists could be synthesized, assigned symbols, partitioned into FPGAs, automatically instrumented with TAI IP blocks, and placed and routed. Software development could begin as soon as a prototype was ready, including using the SoC prototype to communicate with a target interface at hardware speeds – a nearly impossible task using only host-based simulation.

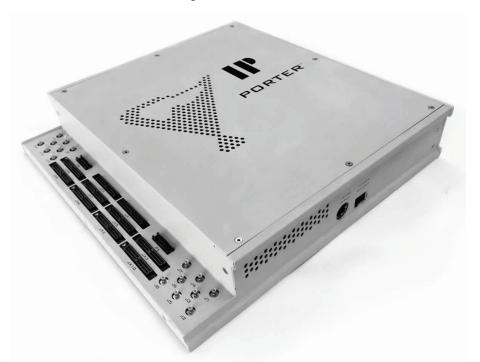

In May 2005, S2C announced its first product at the Design Automation Conference (DAC). The IP Porter system supported SoC designs of up to 3M gates with four Xilinx XC2VP100 FPGAs. It connected to a host via USB 2.0, where the TAI Compiler and Navigator software packages ran. TAI Compiler automated creation of TAI IP modules and libraries, including encryption if desired. Navigator provided links to System C models and SCE-MI transactors connecting event-driven simulation tools on the host with points in the FPGAbased prototype.

Beta customers working with the product estimated their design time was cut by 3 to 6 months. Productivity gains came not so much from the initial setup of a prototype, but from a significant reduction in iteration time as debug and analysis uncovered changes and improvements. TAI IP enabled reconfiguring only the part of the design where changes were made, speeding up the synthesis. Image 2-1: S2C IP Porter

Second-generation product beginning in 2006 moved to a new hardware arrangement with high-performance Mictor connectors allowing stacking of TAI logic module boards each with one or two Xilinx Virtex-4 FPGAs. These connectors also enabled direct addition of a library of expansion modules for memory, video and audio interfaces, logic analyzer breakouts, and more, and allowed customer I/O designs to be added easily.

2007 brought new IP partners, most notably processor core vendors Tensilica and CAST. Work continued on SCE-MI with Hitachi and other co-modeling projects with Asian customers, and a new office opened in Shenzhen to support the growing SoC community in China. In 2008, the TAI IP patent was granted in the US, and the TAI logic modules received the latest Xilinx Virtex-5 FPGAs. Host software was unified under the TAI Player name, with expanded logic analysis and SCE-MI co-modeling. <sup>31</sup>

#### PROTOTYPICAL: The Emergence of FPGA-based Prototyping for SoC Design

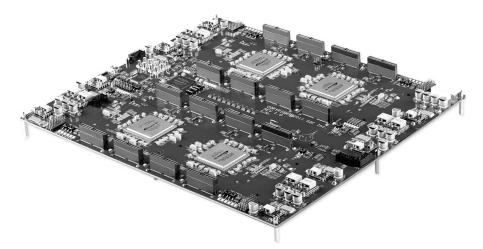

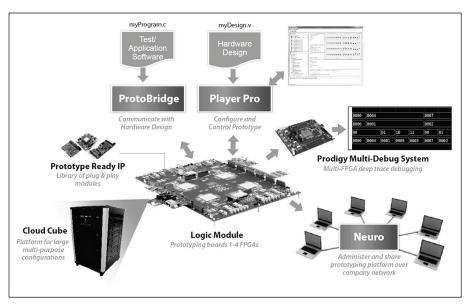

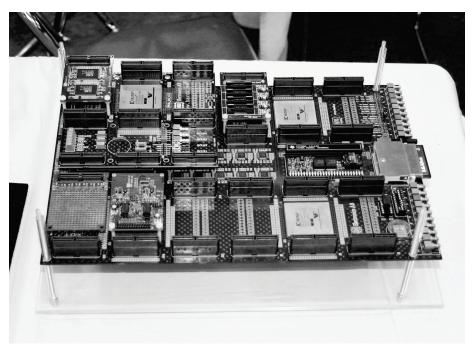

By 2010, the fourth generation logic module based on dual Xilinx Virtex-6 FPGAs appeared, along with a first – support for Altera FPGAs with a dual Stratix IV Logic module, unique among the major FPGAbased prototyping vendors. Design sizes accommodated on a single module topped 15M gates, and module stacking pushed that higher. More modules were added to the accessory library, including PCIe and Gigabit Ethernet. Larger Altera-based systems released in 2011, with the Quad S4 TAI Logic Module carrying four Altera Stratix IV 820 FPGAs upping the capacity to 32.8M gates. <sup>32, 33, 34</sup>

Image 2-2: S2C Quad S4 TAI Logic Module

To handle larger designs and faster verification, S2C also announced a x4 PCIe Gen2 host interface board in 2011, and continued expansion of its Prototype Ready accessory library. Xilinx Virtex-7 logic modules released in 2012, along with ARM1176 and ARM926 Global Unichip Corporation (GUC) Test Chip modules with external AMBA interfacing for ARM designers to quickly incorporate merchant cores. <sup>35, 36, 37</sup>

2013 saw the addition of more logic modules based on the Xilinx Zynq-7000 All Programmable SoC with its integrated dual ARM Cortex-A9 cores. With up to four Zynq-7000 parts on one board, plus a high-frequency LVDS pin multiplexing scheme, a single board could handle up to 80M gates. New Prototype Ready modules added HDMI, GTX transceiver interfacing, and other support around the Zynq-7000.

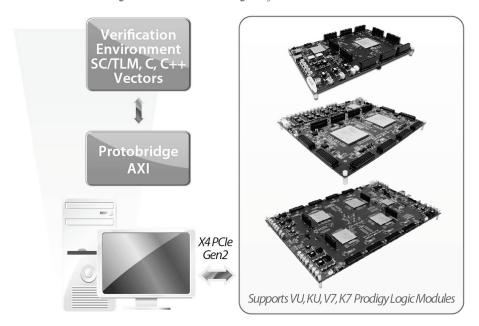

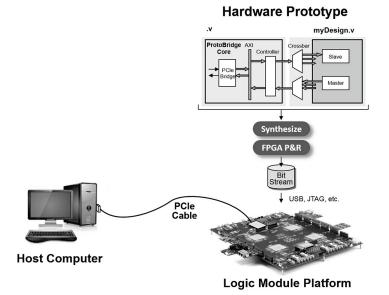

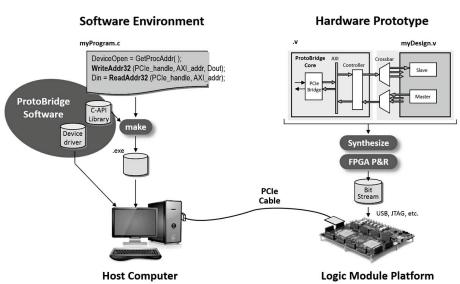

ProtoBridge AXI capability came in 2014, providing native AXI transactors suitable for advanced ARM designs and other IP adopting AXI. <sup>38, 39</sup>

## Taking on the Cloud

S2C continues its expansion under founders Nakama, now CEO, and Chene, now Chairman and CTO. In 2014, new offices opened in Japan and Korea, and a round of \$4.6M Series C financing reinforces R&D and sales and support channels development. Keeping pace with the Xilinx roadmap for larger and faster parts, including the latest Virtex UltraScale 440 FPGA, is just part of the strategy.

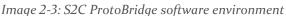

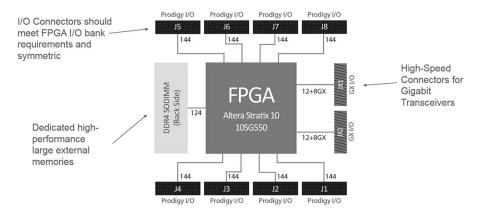

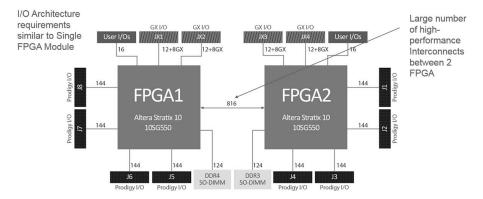

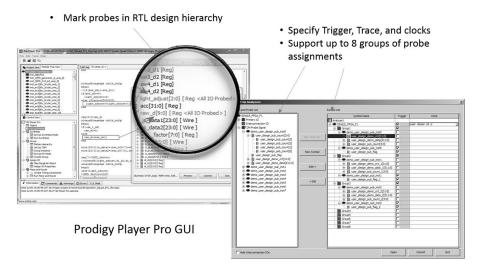

In April 2015, S2C announced a new brand: Prodigy. In many ways, the story remains the same under a new name. Prodigy unifies the offering of FPGA logic modules, Player Pro partitioning and configuration software, ProtoBridge system-level simulation link tool, and the library of Prototype Ready modules now numbering over 80 designs. In other ways, Prodigy marks a new beginning. <sup>40</sup>

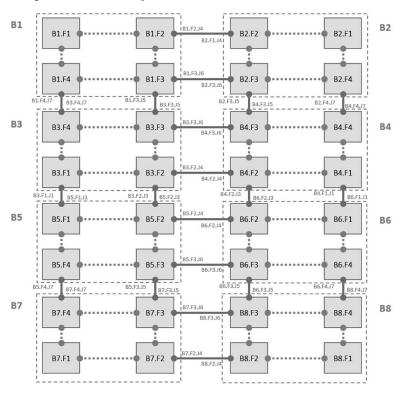

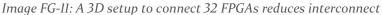

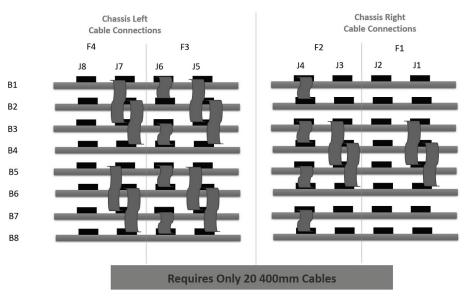

For DAC 2015 in June, ten years after introducing its first product to the public, S2C unveiled a new concept in scalability. Prodigy Cloud Cube introduces a capacity breakthrough providing up to 1.4B gates in a single chassis with up to 32 FPGAs. Simultaneous access for up to 16 engineers is supported, with remote access via Ethernet. Configuration of the platform itself is automatic, with detection of installed logic modules, cabling, and daughter cards, along with self-tests to isolate issues. <sup>41</sup>

S2C's focus on Asia continues to increase, with a new R&D and manufacturing center in Taiwan opened in October 2015. With energy in mobile shifting from flagship smartphones into mid-range devices, and new ideas appearing daily in wearables and the IoT, more designs are starting with a wider variety of hardware IP and software support. Asia is at the epicenter of many of these changes, increasing the need for a distributed FPGA-prototyping solution made for design teams and IP providers to collaborate from wherever they happen to be based.

Scalability also remains important. Single FPGA logic module solutions are now large enough to hold many designs. The ability to use the same

tool set and FPGA-based prototyping methodology from the latest Single KUII5 Prodigy Logic Module introduced in January 2016 all the way up to the Prodigy Cloud Cube is essential for SoC design team productivity. <sup>42</sup>

Image 2-5: S2C Cloud Cube 32

Now serving over 200 customers, S2C has delivered innovation by staying close to its users. Extra handholding required in the first generation has now turned into a competitive advantage in later generations. By looking closely at each step in the SoC design phase, enhancements in S2C FPGA-based prototyping tools are discovered, removing friction and increasing capability and efficiency.

## NOTES

<sup>29</sup> "Scalable reconfigurable prototyping system and method", US Patent 7353162, April 1, 2008, <u>http://www.google.com/patents/US7353162</u>

<sup>30</sup> "S2C delivers breakthrough FPGA-based ESL Design with TAI IP", Design & Reuse, May 31, 2005, <u>http://www.design-</u>

reuse.com/news/10519/s2c-breakthrough-fpga-esl-design-tai-ip.html <sup>31</sup> "A New Era for SoC Prototyping Flow: From System Architecture Plan

to Verification", S2C presentation by Mon-Ren Chene, January 15, 2009,

http://www.digitimes.com.tw/tw/B2B/Seminar/Service/download/0519 801150/DTF 980115 Track1 04.pdf

<sup>32</sup> "S2C Announces 4<sup>th</sup> Generation Rapid SoC Prototyping Solution",S2C press release, June 14, 2010,

http://www.s2cinc.com/company/press-releases/2010/s2c-announces-4th-generation-rapid-soc-prototyping-solution

<sup>33</sup> "S2C Announces Virtex-6 Based 4<sup>th</sup> Generation Rapid SoC Prototyping Solution", S2C press release, August 30, 2010,

http://www.s2cinc.com/company/press-releases/2010/s2c-announcesvirtex-6-based-4th-generation-rapid-soc-prototyping-solution

<sup>34</sup> "S2C Releases 32.8 Million Gate SoC/ASIC Prototyping System", S2C press release, April 2I, 2011, <u>http://www.s2cinc.com/company/press-releases/2011/s2c-releases-32.8-million-gate-socasic-prototyping-</u>system

<sup>35</sup> "S2C Announces a Breakthrough Verification Module", S2C press release, June 6, 2011, <u>http://www.s2cinc.com/company/press-</u> releases/2011/s2c-announces-a-breakthrough-verification-module

<sup>36</sup> "S2C Releases Dual Virtex-7 2000T FPGA Rapid SoC Prototyping Hardware", S2C press release, May 31, 2012,

http://www.s2cinc.com/company/press-releases/2012/s2c-releasesdual-virtex-7-2000t-fpga-rapid-soc-prototyping-hardware

<sup>37</sup> "S2C Releases New Prototype Ready ARMII and ARM9 Modules for FPGA-Based Prototypes", S2C press release, June 1, 2012,

http://www.s2cinc.com/company/press-releases/2012/s2c-releasesnew-prototype-ready%E2%84%A2-arm11-and-arm9-modules-for-fpgabased-prototypes

<sup>38</sup> "New Quad Virtex-7 2000T 3D IC Rapid ASIC Prototyping Platform from S2C Optimized for Design Partitioning", S2C press release, January 21, 2013, <u>http://www.s2cinc.com/company/press-</u> releases/2013/new-quad-virtex-7-2000t-3d-ic-rapid-asic-prototypingplatform-from-s2c-optimized-for-design-partitioning

<sup>39</sup> "S2C ProtoBridge AXI Expands FPGA-Based Prototype Usage", S2C press release, June 30, 2014, <u>http://www.s2cinc.com/company/press-releases/2014/s2c-protobridge%E2%84%A2-axi-expands-fpga-based-prototype-usage</u>

<sup>40</sup> "S2C Sets New Standards for FPGA-Based Prototyping with Prodigy Complete Prototyping Platform", S2C press release, April 21, 2015,

http://www.s2cinc.com/company/press-releases/2015/s2c-sets-newstandards-for-fpga-based-prototyping-with-prodigy-completeprototyping-platform

<sup>41</sup> "S2C Prodigy Cloud Cube Enables FPGA Prototyping of 1 Billion Gate Designs", S2C press release, May 26, 2015,

http://www.s2cinc.com/company/press-releases/2015/s2cprodigy%E2%84%A2-cloud-cube%E2%84%A2-enables-fpgaprototyping-of-1-billion-gates-designs

<sup>42</sup> "S2C Expands Kintex UltraScale Prototyping Solutions for Consumerbased IoT and Other Small to Medium Sized Designs", S2C press release, January 11, 2016, <u>http://www.s2cinc.com/company/press-</u> <u>releases/20161/s2c-expands-kintex-ultrascale-prototyping-solutions-</u> <u>for-consumer-based-iot-and-other-small-to-medium-sized-designs</u>

## Chapter 3: Big EDA Moves In

Larger EDA firms are constantly hunting for other product lines to fill out their portfolios. With ASIC and SoC starts accelerating, and smaller firms becoming successful with FPGA-based prototyping technology, the large firms started seeing a gap in their offering. The trick in a large firm acquiring a small firm is to make those focused tools fit in the bigger picture.

In the case of FPGA-based prototyping, first came an acquisition of one of its pioneers by another FPGA tools vendor, which was then in turn swallowed up by a large EDA firm. Those product lines were rebranded, then expanded. When a comprehensive strategy for FPGA-based prototyping systems was published, it drew an immediate a response from a major competitor. As the need grows, competition is heating up.

## A Laurel and HARDI Handshake

In 1987, the IEEE ratified the initial version of its standard IEEE 1076-1987, VHSIC Hardware Description Language. EDA firms rushed to embrace VHDL technology, both to satisfy its major backer – the US Department of Defense and in particular the US Air Force – and to capture the benefits of a high-level language for design and simulation of ASICs. <sup>43</sup>

Consultants in VHDL instantly sprang up. One of those firms was HARDI Electronics AB, launched shortly after the original release of the IEEE standard in 1987. HARDI quickly produced its first all-VHDL design within a few months. They went on to develop extensive expertise, publishing its VHDL Handbook in 1997 reflecting the updated VHDL '93 version of the standard. <sup>44</sup>

As VHDL usage grew, so did the size of ASIC designs performed using it. Simulation, though effective, was falling behind in terms of providing enough speed to run the necessary verification tests on a larger ASIC. Moving the verification tasks into hardware became the path forward. In 2000, HARDI took the next logical step, creating the HARDI ASIC Prototyping System. For several years, the system then just known as HAPS was used in consulting activity for ASIC customer engagements. HARDI coordinated closely with both Xilinx and a relatively new firm formed in 1994, Synplicity, for FPGA synthesis and debug technology including Synplicity's Certify and Identify.

Demand for the HAPS platform rose over the next several years to the point where HARDI began more aggressive external marketing, launching version 2.1 of HAPS (soon to be rebranded as HAPS-10) at the Design Automation and Test in Europe show in March 2003. HAPS 2.1 held up to four Xilinx Virtex-II 8000 FPGAs providing a total of up to 8M gate capacity running at up to 200 MHz. <sup>45</sup>

Image 3-1: HARDI Electronics AB HAPS-FPGA\_2x3

HARDI launched its product in the US at the Design Automation Conference in June 2003, and soon found a major customer in Texas Instruments. A low end version, the single FPGA HAPS-FPGA\_2x3 accommodating up to IM gates, introduced the idea of stackable prototyping modules – with an early version of the HapsTrak interconnect – for scalable capacity and expansion. HAPS-FPGA\_2x3 also had 120 low voltage differential signaling (LVDS) pairs for high-speed I/O.  $^{46}$

The second-generation HAPS-20 debuted in December 2004 with a quad Xilinx Virtex-II Pro configuration, again stackable via HapsTrak. It focused on I/O speed, providing 80 multi-gigabit serial links and 1600 LVDS pairs. The Virtex-II Pro FPGAs also each carried two IBM PowerPC RISC processor cores for real-time software. User I/O was divided into three voltage regions so separate voltages could be used simultaneously. HAPS-20 added built-in self-test capability to assure users of system integrity. <sup>47</sup>

Xilinx Virtex-4 parts appeared on the third-generation HAPS-34 at the ARM Developers Conference in October 2005, a sign that adoption of FPGA-based prototyping among SoC designers was accelerating. HAPS-34 delivered quad FPGAs with 9 I/O voltage regions. Smaller versions quickly appeared, with the single HAPS-31 and the dual HAPS-32 added in March 2006, all based on HapsTrak for stacking "like LEGO<sup>TM</sup> blocks" as the HARDI PR team put it. <sup>48, 49, 50</sup>

## Verification is Very Valuable

For the fourth generation, HARDI made a break with their logical nomenclature, instead skipping to the HAPS-50 series with an introduction in April 2007. The HAPS-52 featured a pair of Xilinx Virtex-5 LX330 FPGAs. It was basically more of the same approach; however, the quad board was not yet available, with only a reference to more boards available in two months. <sup>51</sup>

Almost two months to the day later came a much more surprising announcement. The HAPS-50 news included a quote on the growing partnership between HARDI and Synplicity, including the addition of the new Total Recall debugging technology. The partnership cemented on June 1, 2007 with the news that Synplicity was acquiring HARDI for \$24.2M in cash. <sup>52</sup> In turn, the new and improved Synplicity was suddenly on radar of one of the big three EDA firms: Synopsys. In a slightly more complicated transaction since Synplicity was publicly traded, Synopsys paid around \$227M to acquire Synplicity on March 20, 2008. HAPS was now a Synopsys brand. <sup>53</sup>

Synopsys took a breath to integrate HAPS into their development flow, creating the Confirma Rapid Prototyping Platform including the Synplicity suite and CHIPit technologies acquired from Pro Design in 2008. Syncing up with Xilinx for the Virtex-6 FPGA, Synopsys released the HAPS-60 in April 2010 with a capacity of up to 18M gates. Synopsys began using the HAPS environment for their own DesignWare IP, and was able to pass through those artifacts to customers. They also added support for the UMRbus, a high-speed host interface allowing co-simulation with a HAPS platform. <sup>54</sup>

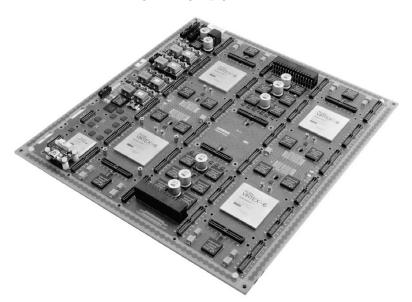

Image 3-2: Synopsys HAPS-64

HAPS-70 appeared in November 2012 with the Xilinx Virtex-7 2000T on nine model variants. An upgrade to HapsTrak 3 improved timedomain pin multiplexing, and the Certify software became "HAPSaware" understanding partitioning and interconnect needs of the hardware, resulting in a 10x productivity improvement. Deep Trace Debug was added with a DRAM module to capture more real-time signals with complex triggering. The UMRbus was also upgraded to support up to 400 MB/sec transfers. <sup>55</sup>

Capacity had long been an objective of HAPS, keeping pace with each successive Xilinx FPGA release. The efforts with DesignWare IP and customers showed how valuable smaller FPGA-prototyping platforms could be, easy to set up for a software developer to work on code or for an IP block developer to work on a single piece of IP prior to integration. Streamlining the larger HAPS-70 platform resulted in the HAPS Developer eXpress, or HAPS-DX, in December 2013. HAPS-DX added an FMC interface for industry-standard daughterboards to add I/O, and ProtoCompiler (formally released in April 2014, replacing the short-lived Confirma tools) extending the flow and hardware awareness in software tools. <sup>56, 57</sup>

## An Either-Or Response

In March 2011 after working in conjunction with Xilinx, Synopsys released the FPGA-Based Prototyping Methodology Manual. Mentor Graphics was (and is) still focused on hardware emulation technology. The third member of the big three, Cadence, was also in hardware emulation but needed some kind of response to the growing FPGAbased prototyping movement.

Cadence had focused on design of FPGA boards themselves. After a multi-year technology agreement proved the concept, Cadence decided to acquire Taray and their FPGA design-in solution in March 2010. Taray pioneered route-aware pin assignment synthesis, optimizing an FPGA design together with the circuit board. This would form an aid for designing an FPGA-based prototyping platform. <sup>58</sup>

The formal response to Synopsys came in a Cadence white paper, "ASIC Prototyping Simplified", in April 2011. In it, they questioned the approach of an off-the-shelf FPGA board to meet a wide variety of ASIC prototyping needs. They suggested instead that customized FPGA boards be built matching the needs of each project, of course using Cadence tools. <sup>59</sup>

It was a time-buying maneuver, just to get the industry talking. A month later in May 2011, Cadence announced a strategy for "app-driven" electronics within its bigger EDA360 vision going beyond just co-verification. Part of that was a new Rapid Prototyping Platform, a family of FPGA boards based on Altera Stratix IV devices. Cadence was attempting to unify its tools and flows, so that a customer could choose either hardware emulation or FPGA-based prototyping and migrate back and forth as needed. <sup>60</sup>

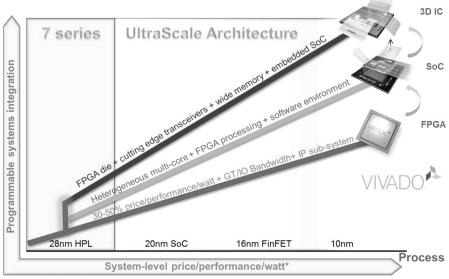

Image 3-3: Cadence Protium

## A Bright Future Ahead

Cadence has a lot of ground to make up in FPGA-based prototyping, but is making investments to try to do just that. In July 2014, they introduced the second-generation Protium rapid prototyping platform, curiously moving to Xilinx Virtex-7 2000T FPGAs matching the competition and increasing capacity by 4x over the first-generation product. The bring-up flow between Palladium hardware emulation and Protium FPGA-based prototyping was further refined, with productivity gains for customers using both environments. <sup>61</sup>

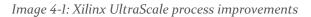

Synopsys has stayed its course as one of the leaders in the field. Moving into the Xilinx UltraScale generation, HAPS-80 launched in September 2015. Synopsys says this gets them to 1.6B ASIC gates with stacked HAPS-80 modules, supported with an improved ProtoCompiler handling the high-speed time-division multiplexing awareness. HAPS-80 runs at 300 MHz for a single FPGA, 100 MHz with non-pin-multiplexed multi-FPGAs, and 30 MHz with pin multiplexing.

Image 3-4: Synopsys HAPS-80

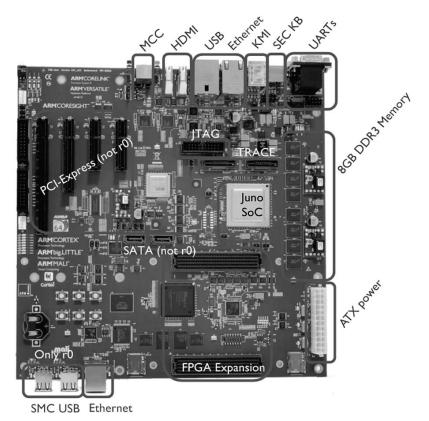

Combined with the efforts of S2C and others including Aldec, The Dini Group, HyperSilicon, Pro Design Electronic GmbH, ReFLEX, and even small prototyping systems from ARM, these developments have moved the art of FPGA-based prototyping systems forward. Next, we'll take a look at where the technology is headed and how designers in segments enjoying a renaissance of design starts can benefit from the ideas.

### NOTES

<sup>43</sup> "1076-2008 – IEEE Standard VHDL Language Reference Manual", IEEE Standards Association,

https://standards.ieee.org/findstds/standard/1076-2008.html <sup>44</sup> "VHDL Handbook", HARDI Electronics AB, 1997,

http://www.csee.umbc.edu/portal/help/VHDL/VHDL-Handbook.pdf

<sup>45</sup> "HARDI Electronics Releases a Real-Time ASIC Prototyping Platform at DATE", HARDI Electronics AB press release, March 3, 2003, http://www.businesswire.com/news/home/20030303005294/en/HAR

DI-Electronics-Releases-Real-Time-ASIC-Prototyping-Platform

<sup>46</sup> "HARDI Electronics Releases a New Single-FPGA Module in the HAPS Prototyping Family", HARDI Electronics AB press release, December 2, 2003,

http://www.businesswire.com/news/home/20031202005773/en/HAR DI-Electronics-Releases-Single-FPGA-Module-HAPS-Prototyping

<sup>47</sup> "HARDI Electronics Unveils Second Generation ASIC Prototyping Platform", HARDI Electronics AB press release, December 13, 2004, <u>http://www.businesswire.com/news/home/20041213005828/en/HARD</u> <u>I-Electronics-Unveils-Generation-ASIC-Prototyping-Platform</u>

<sup>48</sup> "HARDI Electronics Unveils Industry's Most Advanced ASIC Prototyping Platform at the ARM Developers Conference", HARDI Electronics AB press release, October 4, 2005,

http://www.businesswire.com/news/home/20051004005734/en/HAR DI-Electronics-Unveils-Industrys-Advanced-ASIC-Prototyping

<sup>49</sup> "How to Make an ASIC Prototype", Lars-Eric Lundgren, HARDI Electronics AB, Electronic Engineering Journal October 18, 2005, http://www.eejournal.com/archives/articles/20051018 hardi/

<sup>50</sup> "HARDI Electronics Announces Two New Motherboards in The HAPS ASIC Prototyping Family at DATE 2006 (Booth Al)", HARDI Electronics AB press release, March 6, 2006,

http://www.businesswire.com/news/home/20060306005867/en/HAR DI-Electronics-Announces-Motherboards-HAPS-ASIC-Prototyping

<sup>51</sup> "HARDI announces FPGA-based HAPS-50 prototyping system", Max Maxfield, EETimes, April 4, 2007,

http://www.eetimes.com/document.asp?doc\_id=1304157

<sup>52</sup> "Synplicity Announces Agreement to Acquire HARDI Electronics AB", Synplicity press release, June 1, 2007,

### http://www.sec.gov/Archives/edgar/data/1027362/000119312507129831 /dex991.htm

<sup>53</sup> "Synopsys to Acquire Synplicity, Inc.", Synopsys press release, March 20, 2008, <u>http://news.synopsys.com/index.php?item=122910</u>

<sup>54</sup> "Synopsys Introduces the HAPS-60 Series of Rapid Prototyping Systems", Synopsys press release, April 19, 2010,

http://news.synopsys.com/index.php?s=20295&item=123150

<sup>55</sup> "New FPGA-Based Prototyping Solution Delivers Up to 3x System Performance Improvement", Synopsys press release, November 12, 2012, <u>http://news.synopsys.com/index.php?s=20295&item=123433</u>

<sup>56</sup> "Synopsys Extends HAPS-70 Prototyping Family with New Solution Optimized for IP and Subsystems", Synopsys press release, December 16, 2013, <u>http://news.synopsys.com/2013-12-16-Synopsys-Extends-HAPS-70-Prototyping-Family-with-New-Solution-Optimized-for-IP-</u> and-Subsystems

<sup>57</sup> "Synopsys' New ProtoCompiler Software Speeds Time to First Prototype by Up to 3X", Synopsys press release, April 23, 2014,

http://news.synopsys.com/2014-04-23-Synopsys-New-ProtoCompiler-Software-Speeds-Time-to-First-Prototype-by-Up-to-3X

<sup>58</sup> "Cadence Strengthens Leadership in FPGA Design-In Solutions with Acquisition of Taray", Cadence Design Systems press release, March 22, 2010,

http://www.cadence.com/cadence/newsroom/features/pages/feature.a

spx?xml=taray

<sup>59</sup> "ASIC Prototyping Simplified", Cadence Design Systems white paper, April 2011,

http://www.cadence.com/rl/Resources/technical\_papers/asic\_prototyp ing\_tp.pdf

<sup>60</sup> "Cadence Announces Breakthrough in System Development to Meet Demands of 'App-driven' Electronics", Cadence Design Systems press release, May 3, 2011,

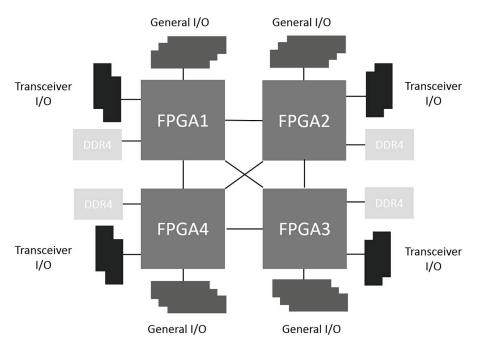

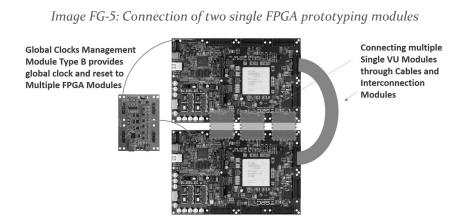

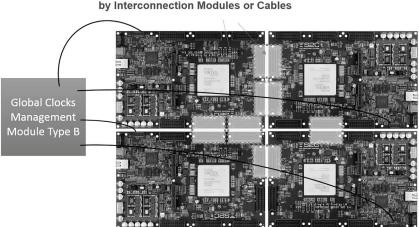

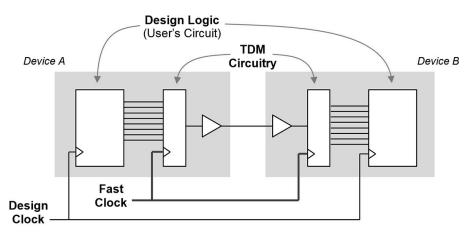

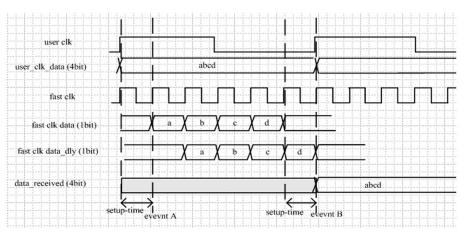

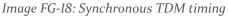

http://www.cadence.com/cadence/newsroom/press\_releases/pages/pr. aspx?xml=050311\_sys\_dev